### SYSTEMES DE VISION INTELLIGENTS: ADEQUATION ARCHITECTURE ALGORITHME, CONCEPTION ET IMPLANTATION MATERIELLES

Julien Dubois

#### ▶ To cite this version:

Julien Dubois. SYSTEMES DE VISION INTELLIGENTS: ADEQUATION ARCHITECTURE ALGORITHME, CONCEPTION ET IMPLANTATION MATERIELLES. Systèmes embarqués. Université de Bourgogne, 2013. tel-02121907

### HAL Id: tel-02121907 https://u-bourgogne.hal.science/tel-02121907

Submitted on 6 May 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Dossier présenté par Julien DUBOIS

Docteur en Electronique

Habilitation à Diriger des Recherches

Intitulé

#### **SYSTEMES DE VISION INTELLIGENTS:**

#### ADEQUATION ARCHITECTURE ALGORITHME, CONCEPTION ET IMPLANTATION MATERIELLES

18 octobre 2013

#### Composition du jury :

- **Pr. Olivier Déforges**, INSA de Rennes Rapporteur

- Pr. Bertrand Granado, Université Pierre et Marie Curie (Paris 6)-Rapporteur

- **Dr. Gilles Sicard**, Université Joseph Fourier Rapporteur

- Dr. François Berry, Université Blaise Pascale de Clermont Ferrand II- Examinateur

- **Pr. Dominique Ginhac**, Université de Bourgogne Examinateur

- Pr. Johel Mitéran, Université de Bourgogne Examinateur

- Pr. Michel Paindavoine, Université de Bourgogne Examinateur

### Remerciements

Que de personnes à remercier pour ces dix ans déjà de recherche au Le2i...

Tout d'abord, je commencerai par Johel Mitéran, Michel Paindavoine et Vincent Vajnovszki pour m'avoir permis de co-encadrer 5 thèses sous leurs directions : expérience au combien enrichissante.

Je souhaiterais remercier Messieurs Déforges, Granado et Sicard pour avoir accepté de rapporter ce manuscrit et Messieurs Berry, Ginhac, Mitéran et Paindavoine pour avoir accepté de l'examiner.

Mes remerciements vont aussi naturellement aux étudiants qu'il m'a été donné d'encadrer au cours de ces années et bien sûr, en particulier, aux doctorants que j'ai co-encadrés avec un très grand plaisir : Romuald Mosqueron, Khalil Khattab, Elfitrin Syahrul, Wajdi Elhamzi et Imen Charfi.

Merci aussi à mes collègues du Le2i avec une pensée particulière à tout le personnel technique Cédric Clerc, Matthieu, Mimi, et toutes les filles du secrétariat, pour leur efficacité, et qui nous permettent de travailler.

Merci bien sûr à mes collègues de l'ESIREM, à toute l'équipe InfoTronique avec qui je travaille tous les jours, merci Christine, Gérard, Patrick, Nader et la liste ... est bien longue...

Merci bien sûr à mes deux complices, Bart et Savério. Merci pour leur bonne humeur, et pour le plaisir de partager avec eux les journées de travail. Et j'ajouterais aussi caro amico che condivide ogni momento, il buono, il brutto e il molto buono (mi dispiace che non ero in grado di scrivere in Calabrese) ... mais, sans doute ai-je bu trop de bon café italien!

Évidemment, merci à ma toute ma famille, qui par sa joie de vivre et l'amour qu'elle m'apporte chaque jour, est la source de mon énergie. Merci.

Et puis surtout, j'espère que je n'oublie personne...

### Sommaire du dossier

| S  | ommai      | re du dossier                                                          |    | 2  |

|----|------------|------------------------------------------------------------------------|----|----|

| T  | able de    | es figures                                                             |    | 5  |

| Ir | ntroduc    | ction générale                                                         |    | 6  |

| Р  | artie1 :   | Dossier administratif                                                  |    | 7  |

| 1  | Intro      | oduction                                                               |    | 9  |

| 2  | Curr       | iculum Vitae                                                           |    | 11 |

|    | 2.1        | Fonctions Actuelles                                                    | 11 |    |

|    | 2.2        | Formation Universitaire                                                | 12 |    |

|    | 2.3        | Parcours Professionnel                                                 | 12 |    |

|    | 2.4        | Bilan des publications scientifiques                                   | 13 |    |

|    | 2.5        | Renseignements complémentaires                                         | 13 |    |

| 3  | Syntl      | hèse des activités pédagogiques & administratives liées à la pédagogie |    | 15 |

|    | 3.1        | Enseignement et responsabilités de module                              | 15 |    |

|    | 3.2        | Synthèse des activités administratives liées à la pédagogie            | 17 |    |

| 4  | Rayo       | onnement, animations et responsabilités scientifiques                  |    | 19 |

|    | 4.1        | Au niveau local                                                        | 19 |    |

|    | 4.2        | Au niveau national et international                                    | 19 |    |

|    | <b>√</b> 0 | rganisation et de colloques                                            | 20 |    |

| 5  | Enca       | drements de thèses et de DEA                                           |    | 21 |

|    | 5.1        | Thèses soutenues (4)                                                   | 21 |    |

|    | 5.2        | Thèse en cours (1)                                                     | 22 |    |

|    | 5.3        | Encadrements de Master Recherche                                       | 22 |    |

| 6  | Activ      | vités contractuelles                                                   |    | 23 |

|    | 6.1        | Contrats publics retenus :                                             | 23 |    |

|    | 6.2        | Contrats publics soumis ou non retenus (2 soumis, 4 non retenus)       | 24 |    |

|    | 6.3        | Contrats privés & transfert de technologies                            | 26 |    |

| 7  | Colla      | aborations scientifiques                                               |    | 29 |

|    | 7.1        | Collaborations internationales :                                       | 29 |    |

|        | 7.2             | Collaborations nationales :                                                                                                                  | 29    |    |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|----|

| 8      | Publ            | ications et Communications                                                                                                                   | ••••• | 31 |

|        | 8.1             | Récapitulatif                                                                                                                                | 31    |    |

|        | 8.2             | Publications dans une revue internationale (17)                                                                                              | 32    |    |

|        | 8.3             | Livres (1)                                                                                                                                   | 33    |    |

|        | 8.4             | Revues de vulgarisation (1)                                                                                                                  | 33    |    |

|        | 8.5             | Articles soumis dans une revue internationale (1)                                                                                            | 33    |    |

|        | 8.6             | Conférences internationales (41)                                                                                                             | 33    |    |

|        | 8.7             | Conférences nationales (10)                                                                                                                  | 36    |    |

|        | 8.8             | Autres présentations internationales (5)                                                                                                     | 36    |    |

| 9      | Réca            | pitulatif des travaux de recherche et responsabilités administratives                                                                        |       | 37 |

|        | 9.1             | Publications                                                                                                                                 | 37    |    |

|        | 9.2             | Encadrement de thèse, master recherche et tutorat stage ingénieur                                                                            | 37    |    |

|        | 9.3             | Activités contractuelles                                                                                                                     | 37    |    |

|        | 9.4             | Responsabilités administratives                                                                                                              | 37    |    |

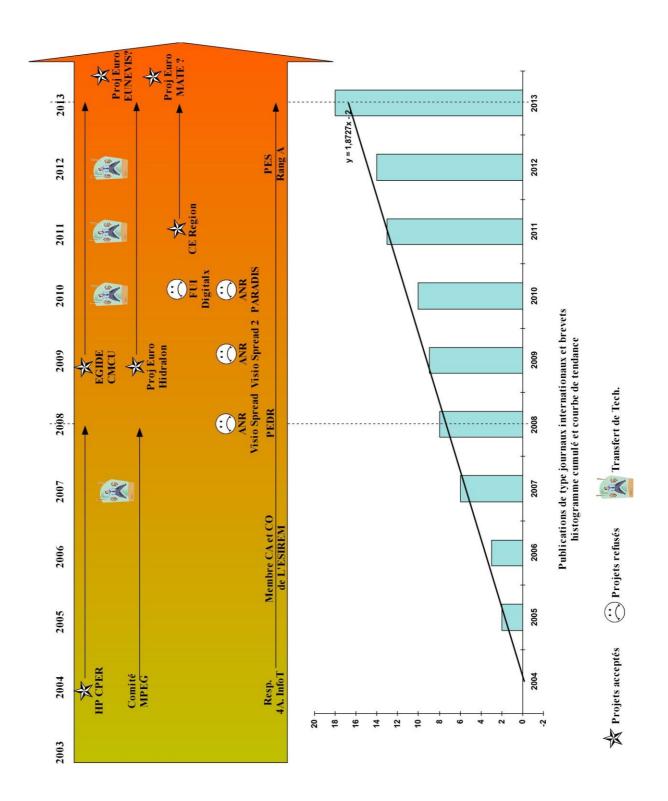

|        | 9.5<br>d'ingéi  | Diagramme temporel résumé des activités de recherche et administratives au sein du cy                                                        |       |    |

| Pa     | artie 2         | Dossier de recherche                                                                                                                         |       | 39 |

| 1      | Intro           | ductionduction                                                                                                                               |       | 41 |

| 2      | Déve            | eloppement de nouvelles méthodes et mise en œuvre                                                                                            | ••••• | 43 |

|        | 2.1             | Contexte scientifique                                                                                                                        | 43    |    |

|        | 2.2             | Chaîne de compression d'images incluant des transformées combinatoires                                                                       | 43    |    |

|        | 2.3             | Analyse de scènes vidéo pour la détection de chutes                                                                                          | 46    |    |

|        | 2.4<br>« intell | Estimation du mouvement pour images multi-exposées : application à l'épandage igent » d'engrais                                              | 48    |    |

|        | 2.5             | Synthèse personnelle sur la recherche de nouvelles méthodes et leur mise en œuvre                                                            | 50    |    |

|        | 2.6             | Bibliographie relative à ce chapitre                                                                                                         | 51    |    |

|        | 2.7             | Publications jointes                                                                                                                         | 51    |    |

| 3<br>A |                 | eloppement d'accélérateurs matériels dans une démarche « Adéquation Algorithn<br>ture » : définition, modélisation, validation, implantation |       | 97 |

|   | 3.1          | Contexte scientifique                                                                                      |     |

|---|--------------|------------------------------------------------------------------------------------------------------------|-----|

|   | 3.2          | Plateforme de co-traitement destinée à la validation d'accélérateurs matériels97                           |     |

|   | 3.3<br>modél | Implantation d'accélérateurs matériels dédié à la reconnaissance de visages à partir de isation en SystemC |     |

|   | 3.4<br>compr | Implantation d'accélérateurs matériels pour l'estimation du mouvement dédiés la ession vidéo               |     |

|   | 3.5<br>comm  | Prototypage rapide d'accélérateurs matérielles : génération automatique d'interfaces de unication          |     |

|   | 3.6          | Synthèse personnelle sur la conception d'accélérateurs matériels                                           |     |

|   | 3.7          | Bibliographie relative à ce chapitre                                                                       |     |

|   | 3.8          | Publications jointes                                                                                       |     |

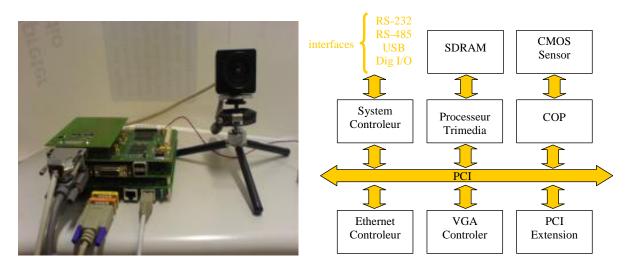

| 4 | Cond         | ception et implantation d'architectures innovantes de caméras intelligentes                                | 153 |

|   | 4.2          | Conception d'une caméra rapide intelligente haute résolution                                               |     |

|   | 4.3          | Caméra intelligente à unité de traitement hétérogène SW/HW                                                 |     |

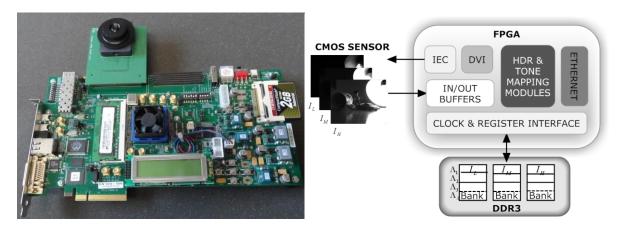

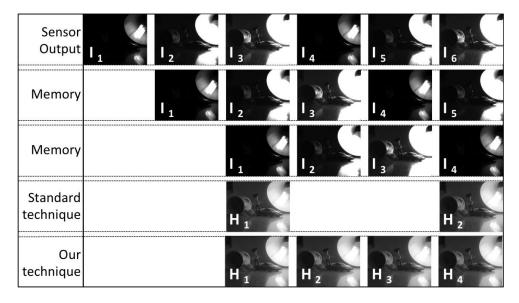

|   | 4.4          | Caméra intelligente pour la haute dynamique                                                                |     |

|   | 4.5          | Synthèse personnelle sur la conception et la réalisation de caméras intelligentes 161                      |     |

|   | 4.6          | Bibliographie relative à ce chapitre                                                                       |     |

|   | 4.7          | Publications jointes                                                                                       |     |

| 5 | Cond         | clusions & perspectives de recherche                                                                       | 191 |

|   |              |                                                                                                            |     |

# Table des figures

| Figure 1 : Insertion de la transformée de Burrows-Wheeler au sein d'une chaîne de compression                                                                                        | de    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| données                                                                                                                                                                              | 44    |

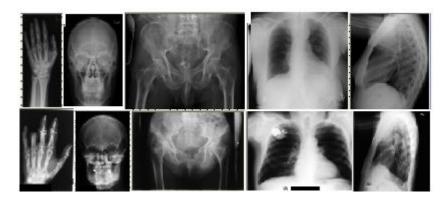

| Figure 2 : IRMA - base de données médicale ouverte à la communauté                                                                                                                   | 45    |

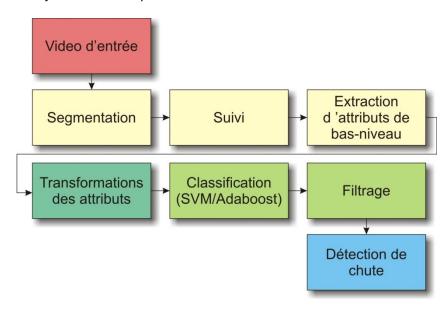

| Figure 3. Représentation schématique de la méthode de détection de chutes                                                                                                            | 46    |

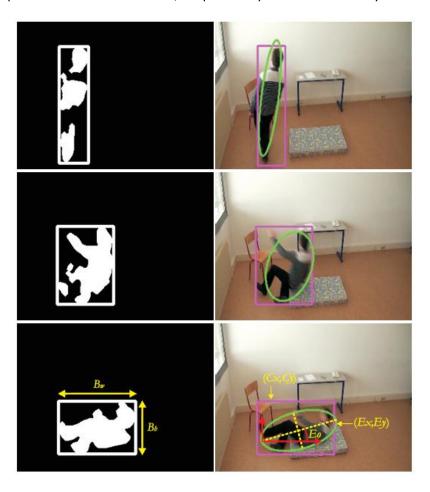

| Figure 4 : Images traitées et extraites d'une scène de chute disponible dans la base de données ouverte à la communauté                                                              | 47    |

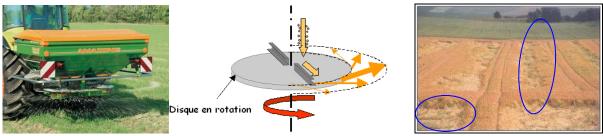

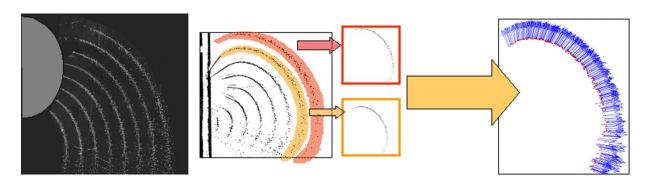

| Figure 5. Estimation des vitesses des granules de fertilisant avec une illustration de cette dernière deux images acquises consécutivement dans le temps (F. Cointault; S. Villette) |       |

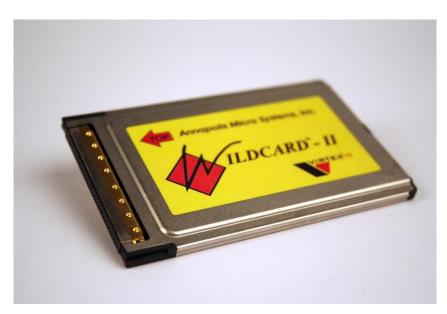

| Figure 6 : Une PC-card à base de FPGA – La Wildcard                                                                                                                                  | 98    |

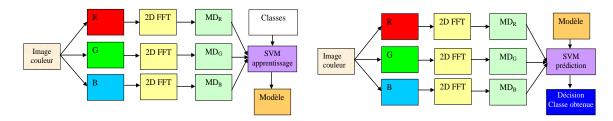

| Figure 7. Phase d'apprentissage et phase de décision                                                                                                                                 | . 100 |

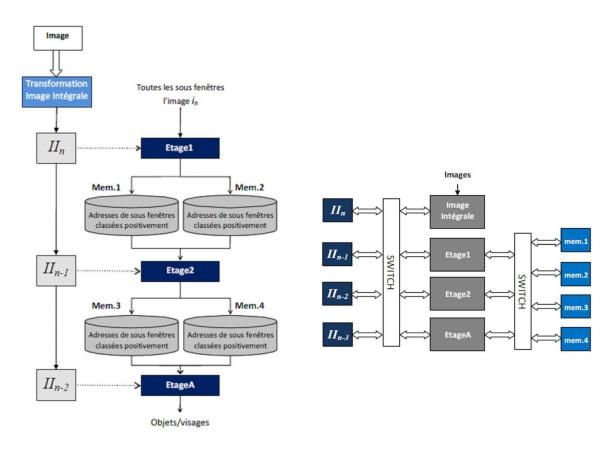

| Figure 8. Exploitation du parallélisme de données dans la cascade de boosting                                                                                                        | . 102 |

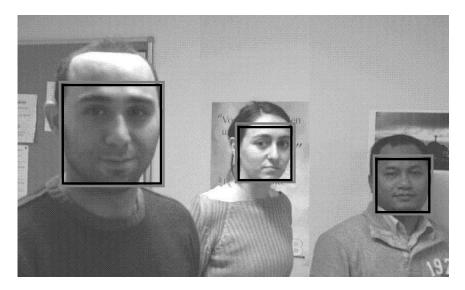

| Figure 9. Détection de visages obtenue à partir de l'architecture proposée                                                                                                           | . 103 |

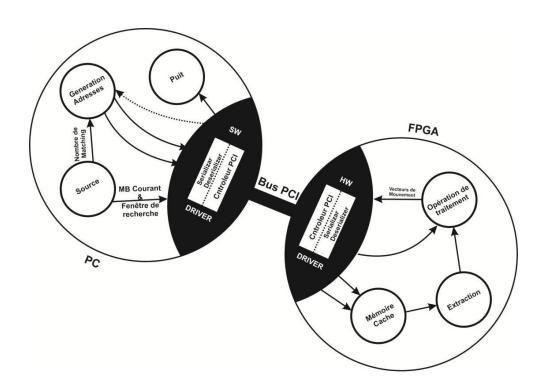

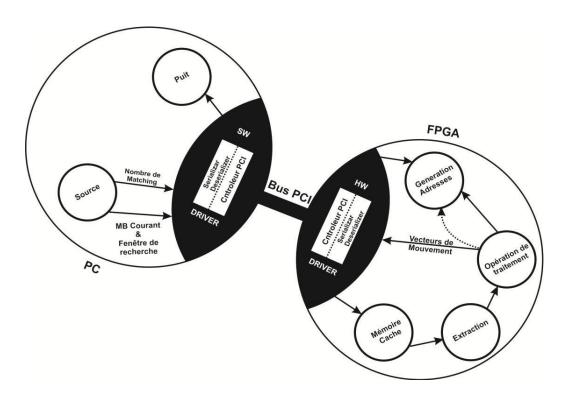

| Figure 10. Implantation matérielle/logicielle de l'estimation de mouvement                                                                                                           | . 108 |

| Figure 11. Implantation matérielle de l'estimation de mouvement                                                                                                                      | . 108 |

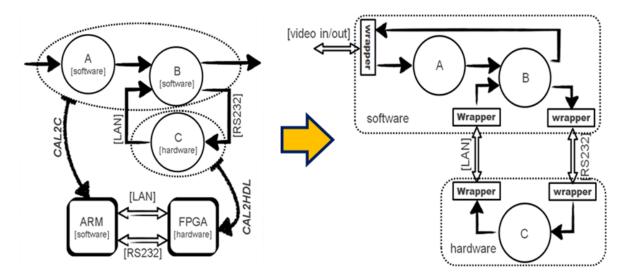

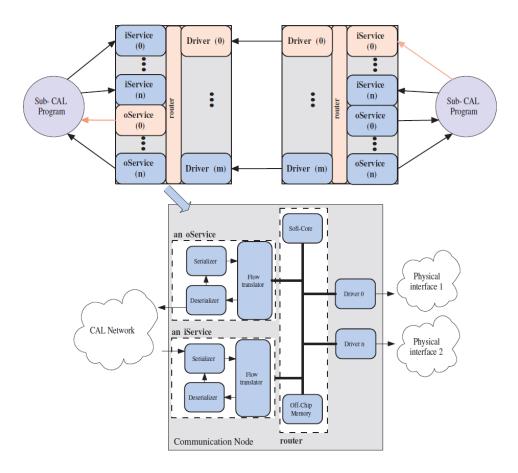

| Figure 12. Modélisation flot de donnée et définition des interfaces communication                                                                                                    | . 109 |

| Figure 13. Evolution du nœud de communication                                                                                                                                        | . 110 |

| Figure 14. Caméra rapide intelligente à haute résolution                                                                                                                             | . 154 |

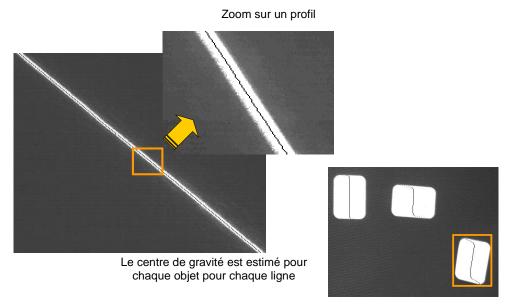

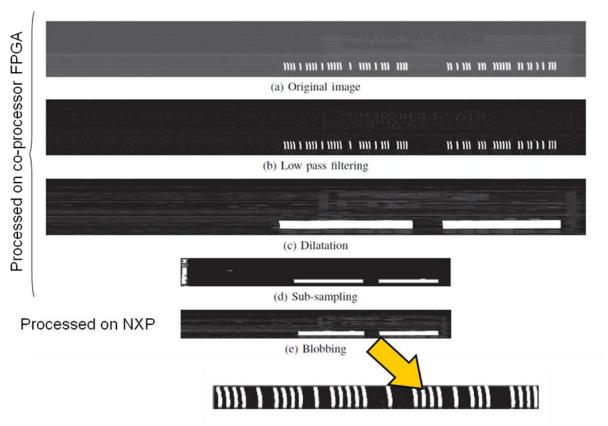

| Figure 15. Chaîne de traitement pour l'extraction de centre de gravité                                                                                                               | . 155 |

| Figure 16. Caméra intelligente à élément de calcul hétérogène et architecture globale développé                                                                                      |       |

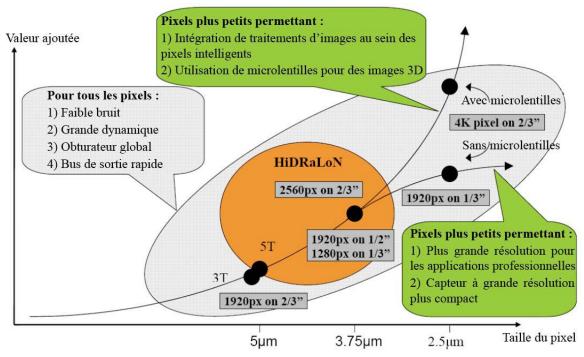

| Figure 17 Différents champs d'applications du projet HiDRal oN                                                                                                                       | 160   |

#### Introduction générale

Les travaux présentés dans le cadre de cette Habilitation à Diriger des Recherches s'inscrivent à la fois dans la problématique dite d'« Adéquation Algorithme Architecture » (A³) mais aussi « Systèmes embarqués », de la section 61 du CNU « Génie informatique, automatique et traitement du signal » . De fait, ces activités de conception de systèmes électroniques s'inscrivent également dans les champs disciplinaires de la section 63 du CNU « Electronique, Optronique et Systèmes » tels que « Composants et systèmes électriques », « Instrumentation » ou « Traitement du signal appliqué ».

Ils ont pour objectif commun la mise en œuvre de systèmes principalement matériels et mais aussi logiciels dédiés à la vision artificielle à fortes contraintes en termes de temps d'exécution. Ces systèmes matériels reposent principalement sur des capteurs d'images spécifiquement développés en technologie CMOS et interfacés avec des structures de calculs plus traditionnelles telles que des FPGA ou des DSP.

### Partie1:

### Dossier administratif

#### 8 Publications et Communications

Les paragraphes suivants sont consacrés à la présentation exhaustive de toutes les publications et communications réalisées depuis 2000. Le classement a été fait en six catégories :

- Publications dans une revue internationale :

- Brevet

- Chapitres de livre

- Communications dans un congrès international avec actes

- Communications dans un congrès national avec actes

- Autres présentations internationales

A titre d'information, les publications internationales soumises et les publications en cours de rédaction ont été également ajoutées en fin de liste.

#### 8.1 Récapitulatif

| Publications dans une revue internationale : | 17( + 1 soumise) |  |

|----------------------------------------------|------------------|--|

| Brevets en cours de dépôt :                  | 1                |  |

| Chapitres de livres :                        | 1                |  |

| Revue de vulgarisation                       | 1                |  |

| Conférences internationales :                | 41               |  |

| Conférences nationales :                     | 10               |  |

| Workshop (contributions MPEG)                | 5                |  |

**76**

Total des publications :

#### 8.2 Publications dans une revue internationale (17)

- [R1] Imen Charfi, Johel Mitéran, Julien Dubois, Mohamed Atri, Rached Tourki, "Optimised spatio-temporal descriptors for real-time fall detection: comparison of SVM and Adaboost based classification", Journal of Electronic Imaging (JEI), 2013, In Press

- [R2] Wajdi Elhamzi, Julien Dubois, Johel Mitéran, Mohamed Atri, Barthélémy Heyrman, Dominique Ginhac, "Efficient smart-camera accelerator: an configurable motion estimator dedicated to video codec", Journal of System Architecture, Ed. Elsevier, 2013, In Press

- [R3] Tomasz TOCZEK, Faouzi HAMDI, Barthélémy HEYRMAN, Julien DUBOIS, Johel MITERAN, Dominique GINHAC, "Scene-based non-uniformity correction: from algorithm to implementation on a smart camera", Journal of Systems Architecture, (2013) 1-18, 2013, In Press

- [R4] Wajdi Elhamzi, Julien Dubois, Johel Mitéran, Mohamed Atri, "An Efficient Low-cost FPGA Implementation of a Configurable Motion Estimation for H.264 Video Coding", Journal of Real-Time Image Processing (JRTIP), August 2012

- [R5] Bilal Hijazi, Jurgen Vangeyte, Frédéric Cointault, Julien Dubois, Sébastien Coudert, Michel Paindavoine, Jan Pieters, "Two-step cross correlation based algorithm for motion estimation applied to fertilizer granules motion during centrifugal spreading", Optical Engineering, Vol.50, Number 6, June 2011.

- [R6] Elfitrin Syahrul, Julien Dubois, Vincent Vajnovski, "Combinatorial Transforms: Application in Lossless Image Compression", Journal Of Discrete Mathematical Sciences & Cryptography, Editor TARU, Vol. 14, Number 2, pp 129-147, april 2011

- [R7] Richard Thavot, Romuald Mosqueron, Julien Dubois and Marco Mattavelli, "Generation of Hardware/Software systems based on CAL dataflow description", Algorithm-Architecture Matching for Signal and Image Processing, Best papers from Design and Architectures for Signal and Image Processing 2007 & 2008 & 2009, Series Lectures Notes in Electrical Engineering, Vol. 73, Springer Verlag, pp 275-292, jan. 2011.

- [R8] Bilal Hijazi, Frédéric Cointault, Julien Dubois, Sébastien Coudert, Jurgen. Vangeyte, Michel Paindavoine, "Multi-phase cross-correlation method for motion estimation of fertilizer granules during centrifugal spreading", Precision Agriculture, pp 684-702, vol.11, No.6, Nov. 2010.

- [R9] Khalil Khattab, Julien Dubois and Johel Miteran, "Cascade Boosting Based Object Detection from High Level Description to Hardware Implementation", EURASIP Journal of Embedded Systems, Special Issue "Design and Architectures for Signal Image Processing", Hindawi, 12 pages, 2009.

- [R10] Christophe Lucarz, Marco Mattavelli, Julien Dubois, "A platform for the development and the validation of HW IP components starting from reference software specifications", EURASIP Journal of Embedded Systems, Special Issue "Design and Architectures for Signal Image Processing", Hindawi, 16 pages, 2008.

- [R11] Romuald Mosqueron, Julien Dubois, Marco Mattavelli, David Mauvilet, "Smart camera based on an Embedded HW/SW Co-Processor", EURASIP Journal of Embedded Systems, Special Issue "Design and Architectures for Signal Image Processing", Hindawi, 13 pages, 2008.

- [R12] Fethi SMACH, Johel MITERAN, Mohamed ATRI, Julien DUBOIS, Mohamed ABID, Jean Paul GAUTHIER, "An FPGA-based accelerator for Fourier Descriptors computing for color object recognition using SVM", Journal of Real-Time Image Processing (JRTIP), Springer, vol.2, pp. 249-258, 2007.

- [R13] Romuald MOSQUERON, Julien DUBOIS, Michel PAINDAVOINE, "*High-speed smart camera with high resolution*", EURASIP Journal of Embedded Systems, Special Issue "Embedded Vision System", Hindawi, vol. 14, no. 1, Article ID 24163, 15 pages, 2007.

- [R14] Johel MITERAN, Jean-philippe ZIMMER, Michel PAINDAVOINE, Julien DUBOIS, "*Real-time 3D face acquisition using reconfigurable hybrid architecture*", EURASIP Journal on Image and Video Processing, Hindawi, vol. 8, no. 3, Article ID 81387, 6 pages, 2007.

- [R15] Johel MITERAN, Sébastien BOUILLANT, Michel PAINDAVOINE, Fabrice MERIAUDEAU, Julien DUBOIS, "Real-time flaw detection on complex object: comparison of results using classification with SVM, Boosting and Hyper-rectangle based method", Journal of Electronic Imaging, SPIE, vol.15, 2006

- [R16] Fan YANG, Michel PAINDAVOINE, Dominique GINHAC, Julien DUBOIS, "Développement d'un système rapide pour le mosaïquage et la reconnaissance de visages panoramiques", Traitement du Signal, Vol. 22 (No. 5), pp. 549-562, Septembre 2005.

[R17] Johel MITERAN, Jiri MATAS, Elbey BOURENNANE, Michel PAINDAVOINE, Julien DUBOIS "Automatic Hardware Implementation Tool for a Discrete Adaboost-Based Decision Algorithm", EURASIP Journal on Applied Signal Processing, Hindawi, 2005 (7), pp. 1035-1046, 2005

#### 8.3 Livres (1)

[R18] Khalil Khattab, Philippe Brunet, Julien Dubois, Johel Mitéran, "Real Time Robust Embedded Face Detection Using High Level Description", InTech, New Approaches to Characterization and Recognition of Faces, Ed. Peter Corcoran, August 2011.

#### 8.4 Revues de vulgarisation (1)

[R19] Fethi SMACH, Johel MITERAN, Julien DUBOIS, Irène Foucherot, "Les Descripteurs de Fourier Généralisés dans le cadre de la reconnaissance de formes", article paru dans la revue de l'Université de Bourgogne en 2008.

#### 8.5 Articles soumis dans une revue internationale (1)

[R20] Mohammad Ali Mirzaei, Julien Dubois, Darin Tsoupikova, "Run-time Supervised Multistage Classifier: Theory and Implementation on FPGA", IEEE Transactions in Industrial Electronics.

#### 8.6 Conférences internationales (41)

- [C1] Imen CHARFI, Johel Miteran, Julien DUBOIS, Mohamed ATRI, Rached Tourki "Spatio-temporal descriptor for SVM and Adaboost based fall detection", Internataional conference TAIMA, special session on Shape Descriptor and application (IDMA), Hammamet, Tunisia, may 2013

- [C2] Wajdi Elhamzi, Julien Dubois, Johel Mitéran, Mohamed Atri, Rached Tourki, "High Efficiency Architecture of Half-Pel Motion Estimation for H.264 Video Coding", Proceedings of International Conference on Information Processing and Wireless Systems (IP-WIS), Djerba, Tunisia, March 2013.

- [C3] Julien Dubois, **"FPGA-based smart camera : industrial applications"**, Keynote at the 9<sup>th</sup> Portuguese Meeting on Reconfigurable Systems, Institute of Systems and Robotics, University of Coimbra, Portugal, Feb. 2013.

- [C4] Imen CHARFI, Johel Miteran, Julien DUBOIS, Mohamed ATRI, Rached Tourki, "Definition And Performance Evaluation Of A Robust SVM Based Fall Detection Solution" Proceedings of IEEE International Conference on Signal-Image Technology & Internet-Based Systems (SITIS 2012), Italy, November 2012.

- [C5] Wajdi Elhamzi, Julien Dubois, Johel Mitéran, Mohamed Atri, Rached Tourki, "Hardware implementation of a configurable motion estimator for adjusting the video coding", Advanced Concepts for Intelligent Vision Systems (ACIVS2012), Brno, Czech Republic, Sept. 2012

- [C6] Imen Charfi, Wajdi Elhamzi, Julien Dubois, Mohamed Atri, Johel Mitéran, "Video Scene analysis for a configurable hardware accelerator dedicated to Smart Camera", IEEE/ACM First Workshop on Architecture of Smart Camera (sponsored by ICDSC conference), Clermont Ferrand, France, April 2012.

- [C7] Wajdi Elhamzi, Julien Dubois, Mohamed Atri, Richard Thavot, Jérôme Gorin, Johel Miteran and Rached Tourki, "An Efficient Hardware Implementation of Diamond Search Motion Estimation Based on CAL Dataflow Language", The 23rd International Conference on Microelectronics (ICM), Hammamet, Tunisia, December 2011.

- [C8] Elfitrin SYAHRUL, Julien DUBOIS, Asep Juarna, Vincent VAJNOVSKI, "Lossless Compression Based on Combinatorial Transform: Application to Medical Images", International Congress on Computer Applications and Computational Science (CACS), Singapore, Dec, 2010

- [C9] Bilal Hijazi, Frédéric Cointault, Jurgen Vangeyte, Julien Dubois, Michel Paindavoine, Jan Pieters "A 3-D stereovision system for fertilizer granule characterization", International Conference of Agricultural & Biosystems Engineering for a Suitable World (AgEng 2010), Clermont-Ferrand, France, Sept. 2010.

- [C10] Elfitrin SYAHRUL, Julien DUBOIS, Vincent VAJNOVSKI, "Burrows Wheeler Compression Algorithm (BWCA) in Lossless image Compression", International Conference on Soft Computing, Intelligent System and Information Technology (2<sup>nd</sup> ICSIIT), Bali, Indonesia, July 2010.

- [C11] Bilal HIJAZI , Frédéric COINTAULT , Julien DUBOIS , Jurgen VANGEYTE, Michel PAINDAVOINE, "New Power-LEDs based illumination system for fertilizer granule motion estimation", Proceedings of 10<sup>th</sup> International Conference on Precision Agriculture (ICPA2010), Denver, USA, July 2010.

- [C12] Bilal HIJAZI, Jeroen BAERT, Frédéric COINTAULT, Julien DUBOIS, Michel PAINDAVOINE, Jan PIETERS, Jurgen VANGEYTE, "A device for extracting 3D information of fertilizer trajectories", Proceedings of 17<sup>th</sup> Congress of the International Commission of Agricultural Engineering (CIGR2010), Québec, Canada, July, 2010.

- [C13] Julien DUBOIS, Richard THAVOT, Romuald MOSQUERON, Johel MITERAN, Christophe LUCARZ, "Motion Estimation Accelerator with User Search Strategy in an RVC Context", Proceedings of IEEE International Conference On Image Processing 2009 (ICIP09), Cairo, Egypt, Nov. 2009.

- [C14] Richard THAVOT, Romuald MOSQUERON, Julien DUBOIS, Marco MATTAVELLI, "Hardware synthesis of complex standard interfaces using cal dataflow descriptions", Workshop on Design and Architectures for Signal and Image Processing (DASIP09), Sophia Antipolis, France, September 2009.

- [C15] Bilal HIJAZI, Frédéric COINTAULT, Julien DUBOIS, Sylvain VILLETTE, Jurgen VANGEYTE, Fan YANG, Michel PAINDAVOINE, "New high speed image acquisition system and image processing techniques for fertilizer granule trajectory determination", Joint International Agricultural Conference 2009 (JIAC09), Wageningen (Netherlands), July 2009.

- [C16] Richard THAVOT, Romuald MOSQUERON, Mohammad ALISAFAEE, Christophe. LUCARZ, Marco MATTAVELLI, Julien DUBOIS, "Dataflow design of a co-processor architecture for image processing", Workshop on Design and Architectures for Signal and Image Processing (DASIP 2008), Bruxelles (Belgium), November 2008.

- [C17] Elfitrin SYAHRUL, Julien DUBOIS, Vincent VAJNOVSKI, Taoufik SAIDANI, Mohamed ATRI, "Lossless Image Compression Using Burrows Wheeler Transform (Methods and Techniques)", Proceedings of IEEE International Conference on Signal-Image Technology & Internet-Based Systems (SITIS'08), Bali (Indonesia), December 2008.

- [C18] Christophe Lucarz, Julien Dubois, Marco Mattavelli "A Co-design platform for algorithm/architecture design exploration", Proceedings of IEEE International Conference Multimedia and Expo (ICME08), Hannover (Germany), June 2008

- [C19] Frédéric Cointault, Jürgen Vangeyte, Julien Dubois, Jeroen Baert, Cedric Clerc "Highspeed Imaging Systems for Granule Fertilizer Motion Characterization", Proceedings of Agricultural & Biosystems Engineering for a Suitable World (AgEng08), Hersonissos, Crete(Greece), 23-25 June 2008.

- [C20] Khalil Khattab, Julien Dubois, Johel Miteran, "Hardware Implementation of Boosting Based Object Detection Using a High Level Description", IEEE International Symposium on Industrial Electronics (ISIE08), Cambridge (UK), June 2008.

- [C21] Julien Dubois, Romuald Mosqueron, Michel Paindavoine, Cedric Clerc, Khalil Khattab, "High-speed smart camera with embedded feature extactions and profilometry measurements", Optical and Digital Image Processing conference (SPIE08), Strasbourg, France, April 2008.

- [C22] Romuald Mosqueron, Julien Dubois, Marco MATTAVELLI, "Smart camera with embedded co-processor: a postal sorting application", Optical and Digital Image Processing conference (SPIE08), Strasbourg, France, April 2008.

- [C23] Christophe LUCARZ, Marco MATTAVELLI, Julien DUBOIS,"*A HW/SW codesign platform for Algorithm-Architecture mapping*", Workshop on Design and Architectures for Signal and Image Processing, DASIP 2007, Grenoble, France, November 2007.

- [C24] Romuald MOSQUERON, Julien DUBOIS, Marco MATTAVELLI,"High Performance Embedded Co-Processor Architecture For CMOS Imaging Systems", Workshop on Design and Architectures for Signal and Image Processing, DASIP 2007, Grenoble, France, November 2007.

- [C25] Michel PAINDAVOINE, Julien DUBOIS, Romuald MOSQUERON, Barthélémy HEYRMAN, Jérôme DUBOIS, Dominique GINHAC, "*High speed camera with embedded image processing*", 6th International Workshop on Embedded System, September 6-7, 2007, Vaasa, Finland, September 2007.

- [C26] Romuald MOSQUERON, Julien DUBOIS, Michel PAINDAVOINE, "*Embedded Image Processing/Compression For High-Speed CMOS Sensor*", Proceedings of EUSIPCO2006, Florence, Italy, 6 September 2006.

- [C27] Michel PAINDAVOINE, Romuald MOSQUERON, Julien DUBOIS, "High-speed embedded real-time image processing", 27th International Congress on High-Speed Photography and Photonics, SPIE, Xian, China, September 2006.

- [C28] Khalil KHATTAB, Johel MITERAN, Julien DUBOIS, Jiri MATAS, "*Embedded System Study For Real Time Boosting Based Face Detection*", IECON 06, Paris, France, pp. 3461-3465, 2006.

- [C29] Julien DUBOIS, Marco MATTAVELLI, Lionel PIERREFEU, Johel MITERAN, "Configurable motion-estiamtion hardware accelerator module for the MPEG-4 reference hardware description platform", Proceedings of IEEE International Conference On Image Processing (ICIP05), Genova, 2005, September 2005.

- [C30] Michel PAINDAVOINE, Romuald MOSQUERON, Julien DUBOIS, Cédric CLERC, Jean Claude GRAPIN, "*High-speed camera with internal real-time image processing*", SPIE Optics and Photonic (SPIE05), San Diego, California, USA, August 2005.

- [C31] Julien DUBOIS, Marco MATTAVELLI, "*Embedded Co-Processor Architecture and hardware processing modules for CMOS based Image Acquisition*", Proceedings of Journées Francophones sur Adéquations Algorithmes Architecture (JFAAA2005), Dijon, France, January 2005.

- [C32] Johel MITERAN, Jiri MATAS, Julien DUBOIS, Elbey BOURENNANE, "BOOSTING: from data to hardware using automatic implementation tool", EUSIPCO2004, Vienne, Autriche, September 2004.

- [C33] Johel MITERAN, Jiri MATAS, Julien DUBOIS, Elbey BOURENNANE, "Automatic FPGA based implementation of a classification tree", SCS'2004 Signaux, Circuits and Systems, Monastir, Tunisia, pp. 189-192, 18 March 2004.

- [C34] Michel PAINDAVOINE, Romuald MOSQUERON, Julien DUBOIS, Cédric CLERC, Jean Claude GRAPIN, Lionel PIERREFEU, "High-speed camera with internal real-time Image compression", 26th International Congress on High-Speed Photography and Photonics (HSPP04), Alexandria, Virginie, USA, pp. 308-319, sept. 2004.

- [C35] Julien DUBOIS, Marco MATTAVELLI, "*Embedded Co-Processor Architecture for CMOS based Image Acquisition*", Proceedings of IEEE International Conference on Image Processing (ICIP03), Barcelona, 14 September 2003.

- [C36] Lionel LELONG, Guy MOTYL, Julien DUBOIS, Alain AUBERT, Gérard JACQUET, "The smart sensors contribution for measurement by image processing in fluid mechanics", 4th Pacific Symposium on Flow Visualization and Image Processing, Chamonix, France, 3 June 2003.

- [C37] Julien DUBOIS, Gérard JACQUET, Guy MOTYL, Viktor FISCHER, Alain AUBERT, "Design of a binary correlator component and its integration in Round-About architecture for real time motion measurement", 25th International Congress on High Speed Photography and Photonics (HSPP02), 29 September 2002.

- [C38] Julien DUBOIS, Gérard JACQUET, Viktor FISCHER, Guy MOTYL, Robert FOUQUET, "Parallel Architecture for Physical Measurements by Image Processing", 15th Conference on Digital Design on Circuits and Integrated Systems (DCIS'2000), Montpellier, pp. 444-449, 21 November 2000.

- [C39] Viktor FISCHER, Julien DUBOIS, "*Flexible Didactic Card with Embedded Processor*", 15th Conference on Digital Design on Circuits and Integrated Systems (DCIS'2000), pp. 392-396, 21 November 2000.

- [C40] Viktor FISCHER, Julien DUBOIS, "*Realisation of a Parameterised Processor in Reconfigurable Hardware*", Proceedings of IEEE 4th International Conference on Electronics Computers and Informatics 2000, Kosice, Slovakia, pp. 151-161, September 2000.

- [C41] Julien DUBOIS, Gérard JACQUET, Guy MOTYL, Viktor FISCHER, "System for real time motion measurement", Third European DSP Education & Research Conference, Paris, France, September 2000.

#### 8.7 Conférences nationales (10)

- [C42] Wajdi Elhamzi, Imen Charfi, Julien Dubois, Johel Mitéran, Mohamed Atri, Rached Tourki, "Un accélérateur matériel flexible pour l'estimation du mouvement dans le cadre de la vidéo assistance avec détection d'événement", 6ème colloque national du GDR SOC-SIP (System-on-Chip & System-in-Package), Paris, juin, 2012.

- [C43] Michel PAINDAVOINE, Romuald MOSQUERON, Julien DUBOIS, Jean Claude GRAPIN, Cédric CLERC, "Réalisation et architecture d'une caméra rapide intelligente.", 9ème Rencontres Nationales du Réseau des Electroniciens (CNRS), Dijon, 2007

- [C44] Julien DUBOIS, "PowerPC emabrqués et accélérateurs matériels pour cibles de type FPGA", 9ème Rencontres Nationales du Réseau des Electroniciens, Dijon, 2007.

- [C45] Michel PAINDAVOINE, Romuald MOSQUERON, Julien DUBOIS, Cédric CLERC, Jean Claude GRAPIN, "*Analyse en temps réel de la locomotion du petit animal par caméra rapide*", IMVIE-3, June 2006.

- [C46] Romuald MOSQUERON, Michel PAINDAVOINE, Julien DUBOIS, Cédric CLERC, Jean Claude GRAPIN, Johel MITERAN, "*Caméra rapide avec compression embarquée temps réel*", RETINE ELECTRONIQUE, ASIC-FPGA ET DSP POUR LA VISION ET LE TRAITEMENT D'IMAGES EN TEMPS REEL (READ05), Evry, France, 2005.

- [C47] Romuald MOSQUERON, Julien DUBOIS, Michel PAINDAVOINE," Compression embarquée temps réel pour caméras rapides", Manifestation des Jeunes Chercheurs en STIC-(MAJECSTIC 2005), Rennes, France, 2005.

- [C48] Julien DUBOIS, Gérard JACQUET, Frédéric CELLE, Viktor FISCHER, "Round-About une architecture de traitement d'images pour la mesure en temps réel de paramètres physiques", 18ème Colloque GRETSI on Signal and Image Processing, 10 September 2001.

- [C49] Julien DUBOIS, Tardi TJAHJADI, Gérard JACQUET, Sébastien COUDERT, "Mesure temps réel de mouvement avec une précision sub-pixel en PIV à partir d'images binaires", Actes du Colloque Interdisciplinaire en Instrumentation (C2I'2001), Hermès, Paris, France, 1, pp. 441-449, 2001.

- [C50] Julien DUBOIS, Gérard JACQUET, Guy MOTYL," Architecture Parallèle pour la Vélocimétrie par Images de Particules", XVIIIème Colloque Photonique et Imagerie Rapide, Arcueil, France, May 2000.

- [C51] Julien DUBOIS, Guy MOTYL, Frédéric CELLE, Viktor FISCHER,"A non intrusive measurement in real time", Journées Signal et Images pour le contrôle dans l'industrie, May 2000.

#### 8.8 Autres présentations internationales (5)

- [C52] Julien DUBOIS, Barthélémy HEYRMAN, Marco MATTAVELLI, Johel MITERAN, " *Wildcard Platform Vs ML310 Platform in a motion estimation context*" ISO/IEC JTC1/SC29/WG11 M13136 Contribution to AHG on MPEG-4 Part 9, San Jose, USA, April 2007.

- [C53] Julien DUBOIS, Barthélémy HEYRMAN, Marco MATTAVELLI, Johel MITERAN, Romuald MOSQUERON, "Motion estimation Hardware Accelerator with Variable Search Window Size", ISO/IEC JTC1/SC29/WG11 M13136 Contribution to AHG on MPEG-4 Part 9, Montreux, Switzerland, April 2006.

- [C54] Andrew KINANE, Marco MATTAVELLI, Julien DUBOIS, Christophe LUCARZ, "Specification of directory structure for SW, HDL and documentation of MPEG-4 Part 9 Reference HW Description", ISO/IEC JTC1/SC29/WG11 N8059, Contribution to AHG on MPEG-4 Part 9: Reference Hardware,, Montreux, Switzerland, April 2006.

- [C55] Julien DUBOIS, Marco MATTAVELLI, Johel MITERAN, "Motion estimation Hardware Accelerator for reduced-search strategy", ISO/IEC JTC1/SC29/WG11 M12934 Contribution to AHG on MPEG-4 Part 9: Reference Hardware, Bangkok, Thailand, January 2006.

- [C56] Julien DUBOIS, Lionel PIERREFEU, Marco MATTAVELLI, "Motion estimation Hardware Accelerator Implementation for Virtex-II Devices", ISO/IEC JTC1/SC29/WG11 M10821 Contribution to AHG on MPEG-4 Part 9: Reference Hardware, Redmond, USA, July 2004.

# 9 Récapitulatif des travaux de recherche et responsabilités administratives

#### 9.1 Publications

| • | Nombre d'articles publiés dans des revues scientifiques :        | 17 |

|---|------------------------------------------------------------------|----|

| • | Nombre d'articles soumis :                                       | 1  |

| • | Brevet:                                                          | 1  |

| • | Nombre de chapitres de livres:                                   | 1  |

| • | Nombre d'articles publiés dans des conférences internationales : | 41 |

| • | Nombre d'articles publiés dans des conférences nationales :      | 10 |

#### 9.2 Encadrement de thèse, master recherche et tutorat stage ingénieur

| • | Thèses soutenues:            | 4  |

|---|------------------------------|----|

| • | Thèses à soutenir :          | 1  |

| • | Stages de recherche de DEA : | 1  |

| • | Tutorat de stage ingénieur : | 26 |

#### 9.3 Activités contractuelles

| • | Contrats de type public : | 4              |

|---|---------------------------|----------------|

| • | Contrats de type privé :  | 4              |

| • | Montant cumulé :          | 383 <b>k</b> € |

#### 9.4 Responsabilités administratives

- Responsable pédagogique de la 4ème année du Département InfoTronique de l'ESIREM

- Membre élu du conseil d'administration de l'ESIREM

- Membre nommé du conseil d'administration de l'ESIREM

- Membre externe de la Commission de spécialistes de l'Université Blaise Pascale (Clermont Ferrand)

Récapitulatif 38

# 9.5 Diagramme temporel résumé des activités de recherche et administratives au sein du cycle d'ingénieur

### Partie 2:

### Dossier de recherche

Introduction 41

#### 1 Introduction

Outre le besoin pédagogique lié à l'ouverture du département InfoTronique au sein de l'école d'ingénieur ESIREM, d'un point de vue recherche, mon recrutement s'inscrivait pleinement dans la problématique de recherche menée par l'équipe « Architecture » de ce laboratoire. Il s'agissait ainsi à la fois de renforcer la thématique « Adéquation Algorithme Architecture » (A³) du Le2i et en raison de mes expériences antérieures j'ai été rapidement amené à contribuer à des travaux de recherche dans le domaine de « vision intelligente à haute cadence ».

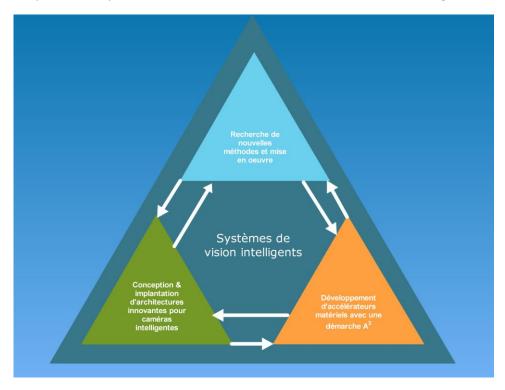

Mon parcours professionnel au sein du Le2i est demeuré fortement lié à la thématique A³ et à celle de vision intelligente au sens large. Au cours de ces dix dernières années (enfin presque...), j'ai pu, aux contacts de mes collègues et grâce à leurs apports, développer une expérience autour des systèmes de vision intelligents et porter cet axe de recherche labellisé « smart camera » au sein du laboratoire le2i dès 2010. Je vais ainsi présenter dans cette partie recherche trois activités qui ont, à mon sens, tout leur place dans la conception et l'implantation de ces systèmes de vision intelligents et présentent des interactions fortes entre elles telle que le schématise la Figure 1 :

- ✓ Développement de nouvelles méthodes pour/ou en vue d'une mise en œuvre dans un système de vision intelligent,

- ✓ Développement d'accélérateurs matériels dans une démarche A<sup>3</sup>,

- ✓ Conception et l'implantation d'architectures innovantes de caméras intelligentes.

Figure 1. Activités réalisées ayant pour objectif la conception de systèmes de vision intelligents

Introduction 42

Pour chacune de ces activités, les contributions pour l'axe de recherche sont ainsi exposées, le bilan en termes de valorisation scientifique est proposé, suivi d'une sélection des publications, jugées significatives.

# 2 Développement de nouvelles méthodes et mise en œuvre

#### 2.1 Contexte scientifique

La conception de systèmes embarqués temps réel, nous amène, en suivant une démarche Adéquation Algorithme Architecture (A³), à la définition de l'architecture des systèmes de visions ou des accélérateurs matériels conjointement à l'étude et à la modification des techniques d'imagerie (de traitement du signal) sélectionnées. Nous pouvons être aussi amenés à travailler de manière plus amont en développant les algorithmes eux-mêmes et en évaluant leurs performances et robustesse indépendamment de la plateforme matérielle support.

Les travaux qui sont ainsi présenté dans ce chapitre s'inscrivent complètement dans ce contexte. Ces études se focalisent sur les thèmes algorithmiques principaux de ma recherche, à savoir la compression, l'analyse d'images et l'estimation du mouvement. Ces traitements sont fondamentaux puisque présents dans un grand nombre de systèmes de vision actuels. Ces traitements seront la base des implantations matérielles proposées dans les chapitres suivants. Trois études sont présentées dans ce chapitre. Dans le cas des deux dernières études, nous avons mis en œuvre une chaîne complète d'acquisition et de traitement, en levant les verrous technologiques liés à l'application considérée. Les trois études sont les suivantes :

- ✓ La première étude se focalise sur une approche originale dédiée à la compression de données. Cette recherche algorithmique pure s'accompagne d'une validation sur plateforme PC standard.

- ✓ La seconde étude propose le développement d'une méthode d'analyse de scènes vidéo permettant la détection de chute. Cette validation a été réalisée dans un premier temps sur une plateforme PC standard puis nous avons réalisé le portage de cette application sur un processeur embarqué dual corps ARM cortex -A9 MPCore (avec OS embarqué distribution Ubuntu).

- ✓ La troisième étude consiste à développer une technique d'estimation du mouvement d'images multi—exposées dans le domaine applicatif de l'agro-équipement. Le challenge réside aussi dans la mise en œuvre d'un système complet de mesure pour l'obtention d'un épandeur d'engrais « intelligent ».

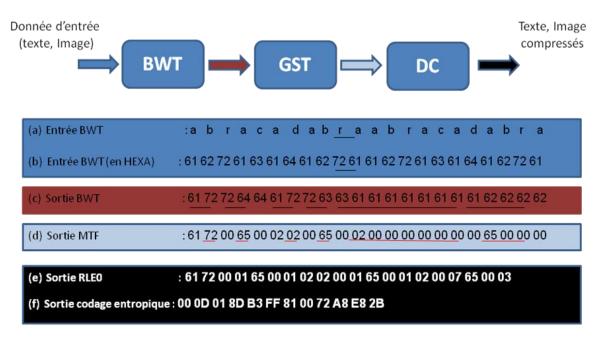

### 2.2 Chaîne de compression d'images incluant des transformées combinatoires

Les méthodes classiques de compression d'image sont communément basées sur des transformées telles que la transformée en Cosinus Discret (DCT) ou encore la transformée discrète en ondelettes. Nous présentons dans ce document une méthode originale basée sur une transformée combinatoire,

celle de Burrows-Wheeler (BWT) [1]. Cette transformée est à la base d'un réagencement des données du fichier servant d'entrée au codeur à proprement parler. Ainsi après utilisation de cette méthode sur l'image originale, les probabilités pour que des caractères identiques initialement éloignés les uns des autres se retrouvent côte à côte sont augmentées. Cette technique est utilisée pour la compression de texte, comme le format BZIP2 qui est actuellement l'un des formats offrant un des meilleurs taux de compression.

La chaîne originale de compression basée sur la transformée de Burrows-Wheeler est composé de 3 étapes, présentées Figure 2. La première étape est la transformée de Burrows-Wheeler elle-même qui réorganise les données de façon à regrouper certains échantillons de valeurs identiques. Burrows et Wheeler conseillent d'utiliser un codage Move-To-Front (MTF) qui va maximiser le nombre de caractères identiques et donc permettre un codage entropique (EC) (principalement Huffman ou un codeur arithmétique). Ces deux codages représentent les deux dernières étapes de la chaîne de compression.

Figure 2 : Insertion de la transformée de Burrows-Wheeler au sein d'une chaîne de compression de données

La méthode présentée est une approche originale intégrant l'utilisation de transformées combinatoires dans une chaîne de compression de données. La méthode est issue des travaux de thèse de Mademoiselle Syahrul Elfitrin. J'ai assuré le co-encadrement de cette thèse dirigée par le Professeur Vincent Vajnovszki. Ces travaux ont bénéficié du support de financier du ministère de la recherche indonésien et de l'ambassade de France en Indonésie.

Nous avons étudié l'état de l'art et réalisé des études empiriques de chaînes de compression basées sur la transformée BWT pour la compression d'images sans perte. Les données empiriques et les analyses approfondies se rapportant à des variantes de MTF et EC. De plus, contrairement à son utilisation pour la compression de texte, et en raison de la nature 2D de l'image, la lecture des données apparaît importante. Ainsi un prétraitement est utilisé lors de la lecture des données et

améliore le taux de compression. Nous avons comparé nos résultats avec les méthodes de compression standard et en particulier JPEG 2000 et JPEG-LS. En moyenne le taux de compression obtenu avec la méthode proposée est supérieur à celui obtenu avec la norme JPEG 2000 ou JPEG-LS. Ainsi sur la base IRMA (base images médicale) [2] présentée Figure 3, les gains moyens sont respectivement de 4,9 et 6,3 % de gain en moyenne sur JPEG-LS et JPEG2K.

Il est important de noter que la valeur moyenne masque l'écart de performances obtenu. Ainsi le taux de compression obtenu avec cette méthode est supérieur à celui obtenu avec JPEG-LS pour seulement 40 % des images de la base. Sur ces images, le gain est alors en moyenne de 20% par rapport à JPEG-LS. Par conséquent, le taux de compression est inférieur pour 60 % des images de la base. Dans ce cas la perte enregistrée au niveau du taux de compression est égale à 3,33 %. Des résultats quasi identiques ont été observés avec le standard JPEG2000.

Aucun critère discriminant entre ces deux classes d'images n'ayant à ce jour été trouvé, nous avons proposé la mise en œuvre d'un double codeur JPEG-LS et la méthode basée la BWT. Le flot de donnée doit alors être compressé en parallèle par les deux codeurs. Le flot compressé de plus petite taille est conservé et marquée en fonction de la méthode de compression utilisée. Dans ce cas, le gain serait alors en moyenne de 8 % par rapport à JPEG-LS.

Figure 3 : IRMA - base de données médicales ouverte à la communauté scientifique

D'un point de vue pratique, une version presque sans perte d'images médicales a aussi été proposée. Une segmentation de la zone critique est alors réalisée. Cette zone est compressée sans perte tandis que le reste de l'image est très fortement compressée avec perte (voir éliminée pour certaines configurations).

Des perspectives existent pour ces travaux, notamment sur deux axes :

- ✓ Le développement d'un accélérateur matériel réalisant de traitement de la transformée de Burrows-Wheeler en temps réel (25 images/s), pour proposer in-fine la réalisation d'un système d'acquisition permettant l'obtention d'un flux compressé sans perte. La conception d'un tel accélérateur demeure un challenge en raison du très nombre de permutations à réaliser séquentiellement.

- ✓ L'utilisation de la méthode par plan de bits et non pas sur la dynamique total de l'échantillon afin de réduire la statistique des échantillons à regrouper.

#### 2.3 Analyse de scènes vidéo pour la détection de chutes

Les applications liées à la vidéo assistance nécessitent une bande passante élevée notamment lorsque la sortie est composée d'informations à la fois bas niveau (pixel, image) et haut niveau (informations extraites automatiquement, comme le nombre de personnes présentes dans la scène, la détection d'événements inhabituels de type chute, etc.). Dans ce contexte, nous étudions un système de détection de chutes adapté à une implantation matérielle permettant de réduire la bande passante finale nécessaire (compression vidéo adaptative). En effet, l'analyse de l'évolution de la scène permet d'adapter la compression dynamiquement en fonction des besoins pour lesquels différents taux de compression peuvent être affectés.

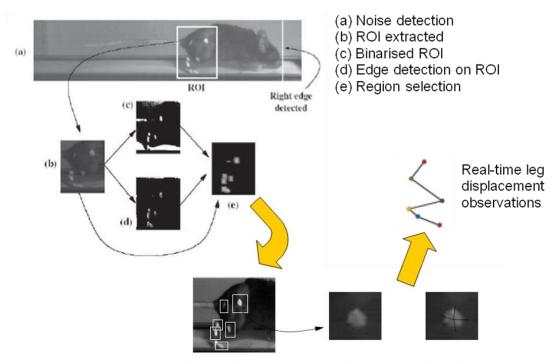

La méthode originale proposée de détection automatique de chutes, nous a permis de définir des descripteurs de chute et d'étudier leurs performances. Ces descripteurs sont calculés à partir de la géométrie de la forme en mouvement dans la scène, et de la transformée de Fourier ou des ondelettes combinés avec des classifieurs de type SVM et Boosting. La représentation schématique de la méthode de détection est représentée Figure 4. L'approche proposée est issue des travaux de thèse de Mademoiselle Charfi Imen. J'ai assuré le co-encadrement de cette thèse réalisé en cotutelle avec l'Université de Monastir. Cette thèse a été dirigée par le Professeur Johel Mitéran. Elle s'appuie sur des études préalables menées conjointement avec le Professeur Mitéran [R12][R15][R17]. Le domaine applicatif est la vidéo assistance. Le projet a été supporté financièrement par le projet EGIDE UTIQUE dont j'ai assuré la responsabilité.

Figure 4. Représentation schématique de la méthode de détection de chutes

De manière plus précise, la détection est basée sur une élimination de l'arrière-plan, un suivi de la personne en mouvement et l'extraction d'attributs de premier niveau (moments, caractéristiques de la boîte englobante, position de l'ellipse englobante de la zone en mouvement, etc.) tels que représentés sur la Figure 5. Au total 14 attributs sont définis puis réduits à 7 par sélection d'attributs de type « Sequential Backward Floating Selection » (SBFS). Une chute étant caractérisée par une variation brutale de certains de ces attributs, nous avons appliqué différentes transformées (dérivées première et seconde, FFT et transformée en ondelette). Les données brutes et ces transformées,

calculées sur une fenêtre temporelle glissante (dont nous avons étudié la taille optimum) forment des attributs de second niveau constituant le vecteur d'entrée du classifieur, qui donne une décision pour cette plage d'images. Nous appliquons de plus à la sortie du classifieur une règle temporelle prenant en compte 18 décisions successives, ce qui correspond à la durée moyenne d'une chute.

Figure 5 : Images traitées et extraites d'une scène de chute disponible dans la base de données ouverte à la communauté

En outre, nous avons constitué une base de 200 vidéos annotées comprenant des chutes et des situations diverses afin de réaliser l'apprentissage puis l'évaluation de la méthode, ainsi que la recherche de la meilleure combinaison possible d'attributs. Cette base de données est ouverte à la communauté scientifique et accessible sur le site <a href="http://le2i.cnrs.fr/Fall-detection-Dataset">http://le2i.cnrs.fr/Fall-detection-Dataset</a>. Afin d'évaluer la robustesse de la méthode au changement de point de vue et d'environnement, les vidéos ont été enregistrées dans 4 locaux différents. Différents protocoles d'évaluation ont été proposés et testés afin d'obtenir une solution réaliste en vu du déploiement au sein d'une habitation personnelle ou encore au sein de structure médicalisée (hôpital, maison de retraite).

Les résultats expérimentaux préliminaires nous permettent de conclure que dans le cas des SVM, la meilleure combinaison d'attributs est constituée des données brutes et de leur dérivée première. Dans ce cas, le meilleur résultat obtenu est une seule fausse alarme constatée sur l'ensemble des vidéos, alors que toutes les chutes sont détectées. Lorsque le test est réalisé sur des vidéos d'un

environnement qui n'a jamais été appris, le nombre de fausses alarmes passe à 4 (rappel : 0.89, précision : 0.94).

Dans le cas du Boosting, les performances finales sont très proches des SVM, (rappel : 0.86, précision : 0.96) et beaucoup mieux adaptées à une implantation matérielle de type FPGA, puisque la fonction de décision est constituée de simples comparateurs qui peuvent être largement parallélisés [R17].

Les contributions de ce travail sont : la constitution d'une base de 200 vidéos annotées, enregistrées en plusieurs endroits ; une analyse de la trajectoire et de la déformation de la forme en mouvement réalisées directement par le classifieur, laissant ce dernier prendre en compte l'aspect temporel de la chute, contrairement à [3], [4]; une comparaison en faveur du Boosting qui permet, à performances de classification comparables, d'envisager une implantation matérielle complète sur FPGA à faible coût, compatibles avec nos objectifs initiaux d'intégration de l'ensemble dans une caméra intelligente. D'autre part, nous avons réalisé l'intégration de la détection de chute sur une cible matérielle de Zynq. L'idée essentielle de ce développement réside dans le prototypage rapide de la méthode sur une plateforme embarqué autonome. Le composant Zyng possède d'une part une architecture hétérogène qui allie un processeur double-cœur et de la logique configurable et d'autre part propose un grand panel d'interfaces de communication. Ainsi, le déploiement d'un OS de type Ubuntu sur cette cible a permis la réutilisation du code original en C/C++ et des bibliothèques associées (principalement OpenCV) ainsi qu'une gestion simplifiée des interfaces de communications. Le système proposé, assimilable à une caméra intelligente, est composé d'une webcam et d'une carte d'évaluation intégrant un composant Zynq. Les communications sont assurées par des liaisons USB et Ethernet respectivement pour les liaisons :

- ✓ entre capteur vidéo et carte d'évaluation

- ✓ entre capteur d'évaluation et l'environnement extérieur.

L'adaptation algorithmique mais aussi la transformation du code dans une version « multi-thread » a permis d'obtenir une intégration performante (environ 10 images/s) de la méthode proposée sur ce système embarqué et autonome. Des perspectives intéressantes demeurent naturellement dans le passage de ces parties de l'algorithme en implantation matérielle dans l'objectif de traiter le flux vidéo en temps réel à 25 images/s.

# 2.4 Estimation du mouvement pour images multi-exposées : application à l'épandage « intelligent » d'engrais

La fertilisation excessive des terres agricoles est considérée comme une contribution majeure au déséquilibre environnemental croissant observé dans les 20 dernières années. Un meilleur contrôle de la précision des méthodes d'épandage limiterait les excès de fertilisant inutilement déversés dans l'environnement. L'objectif de ces travaux est de se concentrer sur le contrôle de l'épandage centrifuge qui représente le mode de fertilisation le plus communément utilisé en Europe (Figure 6).

Figure 6.. a- Un système d'épandage centrifuge commercial (Amazone S.A.); b-principe de l'épandeur centrifuge (S. Villette) ; c-images illustrant des problèmes occasionnés par des mauvaises fertilisations (cercles).

L'utilisation de matériel permettant l'acquisition et le traitement d'images a permis de la définition de nouvelles technologies permettant d'observer et de décrire le comportement des granules de fertilisant durant la phase d'éjection au niveau de l'épandeur centrifuge. La répartition au sol du fertilisant peut ainsi être prédite en utilisant un modèle de vol balistique à condition de pouvoir déterminer, lors de la phase d'éjection, les vitesses et les directions des granules. Nos travaux ont ainsi consisté à proposer l'amélioration d'un système de mesure de ces informations, basé sur de l'imagerie rapide mais aussi sur le système d'illumination stroboscopique spécifique à cette application. Ces travaux ont été portés et initiés par F. Cointault d'AgroSup Dijon avec le soutien du Professeur M. Paindavoine. Ces travaux ont majoritairement été développés lors de la thèse de Monsieur Hijazi Bilal (soutenue en 2012). Cette thèse a été co-encadrée par Monsieur Frédéric Cointault et dirigé par le Professeur Michel Paindavoine. J'ai collaboré sur ces études d'une part sur la définition de la méthode du mouvement en 2D et d'autre part sur la mise en place du système expérimental. Ces méthodes ont été empruntées aux techniques de vélocimétrie par images de particules utilisées en mécanique des fluides. Ces techniques m'étant particulièrement familières puisqu'aux cœurs de mes travaux de thèse. Ces méthodes ont dû être adaptées aux contraintes des images multi-exposées avec large déplacement inter-expositions.

Les images multi-exposées sont ainsi constituées d'une série de jet d'engrais ayant une forme se rapprochant d'arcs tel qu'illustré Figure 7. Chacun d'entre eux doit être identifié et extrait de manière automatique. Une technique basée principalement sur de l'inter-corrélation et réalisée sur de petites zones (typiquement 16x16 ou 32x32) permet de réaliser l'identification et le suivi des particules entre deux jets consécutifs. Cette technique d'estimation du mouvement directement inspirée de la méthode de vélocimétrie par images de particules (P.I.V) a été comparée avec d'autres méthodes en particulier une méthode basée sur les champs de Markov (MRF), mise en œuvre dans les travaux précédemment menés durant la thèse de F. Cointault [5].

Figure 7. Estimation des vitesses des granules de fertilisant avec une illustration de cette dernière sur deux images acquises consécutivement dans le temps (*F. Cointault; S. Villette*).

Les tests ont montré que la méthode basée sur l'inter-corrélation est nettement plus précise que les champs de Markov et garantissait l'obtention d'une précision sub-pixel. Sachant qu'à partir de la résolution spatiale choisie (640x480) et de la distance caméra – épandeur (figée pour des raisons de sécurité du matériel) une erreur d'un pixel entraîne une erreur de prédiction au sol comprise entre 200 et 500 mm, la méthode proposée permet d'obtenir une précision sur les composantes horizontales et verticale de la vitesse comprise entre 0.1 et 0.4 pixels contre une erreur située entre 3 et 9 pixels avec la méthode MRF. La précision sub-pixel a été démontrée par l'utilisation d'images de synthèse modélisant des déplacements contrôlés au niveau des grains de fertilisant. Cette précision sub-pixel permet ainsi d'envisager des résolutions spatiales réduites, avec des caméras standard. La réduction de prix de revient du système résultant est alors nettement inférieure à l'utilisation de caméras rapides possédant des résolutions spatiales supérieures au méga-pixel. Ces améliorations rendent alors envisageable le déploiement de ce type de système, probablement sous la forme de caméras intelligentes, sur les épandeurs classiques. Pour autant, la source lumineuse doit permettre un éclairage uniforme sur une large surface (typiquement 1 m²) de type stroboscopique synchronisé sur le système d'acquisition. Nous avons ainsi développé ce type d'éclairage à base de LED de puissance en vue du déploiement industriel du système de mesure. Ce système d'éclairage a fait l'objet d'un dépôt de brevet.

La transposition de la plateforme 2D à un système de mesure 3D a été investiguée par l'équipe de recherche d'AgroSup en collaboration avec l'institut d'ILVO (Belgique). La mise en place d'un système stéréoscopique a permis une mesure précise des trois composantes des vecteurs vitesses et améliorer ainsi l'estimation de la distribution de fertilisant au sol.

L'intégration du système 2D sur composant de type FPGA est actuellement à l'étude en collaboration avec l'institut d'ILVO. La caméra intelligente qui sera alors obtenue pourra ainsi être déployée sur les épandeurs d'engrais centrifuges

# 2.5 Synthèse personnelle sur la recherche de nouvelles méthodes et leur mise en œuvre

Les méthodes définies ont été développées dans le but de répondre aux contraintes fortes des applications visées. Leur originalité doit être un apport fondamental pour améliorer les performances des systèmes de vision intelligent (bien souvent pour une application donnée). Nous avons toujours développé ces techniques dans l'objectif d'une mise en œuvre au sein d'un démonstrateur. Ainsi une démarche A<sup>3</sup> a accompagné ces développements.

D'autre part, nous réalisons le constat que les modes d'acquisition et généralement fortement lié aux traitements envisagés. La liaison entre acquisition et traitement justifie l'idée même de systèmes dits « intelligents ». Où se situe la limite entre acquisition et traitement ? Cette question est tout à fait légitime dans le cas d'un capteur intelligent! Ainsi la détection d'évènements dans la scène vidéo, comme la détection de chutes, peut permettre de contrôler temporellement le débit d'un codeur vidéo (ou encore la qualité de l'encodage).

Le contrôle en dynamique de l'acquisition comme par exemple l'extraction de zones d'intérêt dans les images s'avère fondamental pour les performances du système global. Ainsi, le contrôle de l'acquisition peut permettre de :

- ✓ simplifier le traitement à mettre en jeu,

- ✓ sélectionner les zones utiles dans l'image à un instant donnée et réduisant par conséquent les bandes passantes nécessaires pour les transmissions des données ou encore le temps de calcul.

La répartition du flot de données entrant vers les différentes unités de traitement pour un fonctionnement en parallèle de ces dernières, s'avère tout aussi fondamental pour obtenir de hautes performances de traitement. Nous essayerons de l'illustrer dans la section 4 qui traite de la définition d'architectures innovantes pour les systèmes intelligents de visions.

Finalement, l'utilisation de cibles matérielles telles que le Zynq permet (avec déploiement d'un OS et une distribution adaptée) la migration rapide vers un prototype opérationnel. Bien sûr, une perte de performance peut être alors observable si aucune optimisation de type logicielle (par exemple une version « multi-thread ») ou matérielle (intégration de certaines fonctionnalité en matériel) n'est réalisée. Pour autant, ces solutions ou plus généralement doivent être considérées pour réduire les temps de développement (souvent très important) du système global. Nous présenterons cette approche en section 3.

#### 2.6 Bibliographie relative à ce chapitre

- [1] M. Burrows and D. J. Wheeler. "A block-sorting lossless data compression algorithm". Technical report, System Research Center (SRC) California, May 10, 1994.

- [2] T. M. Lehmann, M. O. Güld, C. Thies, B. Fischer, K. Spitzer, D. Keysers, H. Ney, M. Kohnen, H. Schubert, and B. B. Wein. Content-based image retrieval in medical applications. 2004.

- [3] C. Rougier, J. Meunier, A. St-Arnaud, J. Rousseau, "Robust Video Surveillance for Fall Detetion Based on Human Shape Deformation", IEEE Transactions on Circuits and Systems for Video Technology, 2011, pp 611-622.

- [4] A. Hervieu, P. Bouthemy, J.P. Le Cadre, "Reconnaissance d'évènements vidéos par l'analyse de trajectoires à l'aide de modèles de Markov", Traitement du signal, 2009, pp 187-197.

- [5] F. Cointault, Automatisation de la mesure du débit d'engrais et trajectographie des granules d'engrais : application à la fertilisation raisonnée dans le contexte de l'agriculture de précision, thèse, 2001

#### 2.7 Publications jointes

Les travaux relatifs à la thématique présentée dans cette section ont permis une valorisation scientifique significative avec notamment la publication de 5 articles dans des journaux scientifiques internationaux, un dépôt d'un brevet et treize présentations dans des conférences internationales.

Une sélection de deux articles récents et publiés dans des revues internationales est proposée :

- [R1] Imen Charfi, Johel mitéran, Julien Dubois, Mohamed Atri, Rached Tourki, "Optimised spatio-temporal descriptors for real-time fall detection: comparison of SVM and Adaboost based classification", Journal of Electronic Imaging (JEI), pp.31, 2013, In Press

- [R5] Bilal Hijazi, Jurgen Vangeyte, Frédéric Cointault, Julien Dubois, Sébastien Coudert, Michel Paindavoine, Jan Pieters, "Two-step cross correlation based algorithm for motion estimation applied to fertilizer granules motion during centrifugal spreading", Optical Engineering, Vol.50, Number 6, pp.13, June 2011.

# 3 Développement d'accélérateurs matériels dans une démarche « Adéquation Algorithme Architecture » : définition, modélisation, validation, implantation

#### 3.1 Contexte scientifique

La définition et l'implantation d'accélérateurs matériels est réalisée dans une démarche d'Adéquation entre Algorithme et Architecture (AAA). Le développement d'architectures innovantes représente le cœur de mes travaux de recherche. J'ai ainsi contribué au développement d'un certain nombre d'architectures innovantes depuis mon intégration au sein du Le2i, parfois en tant qu'initiateur, parfois en tant que participant. De plus, en partant du constat que la conception des systèmes de vision embarqués permet généralement la réutilisation d'un certain de nombre de fonctionnalités (aussi bien en termes de traitement que de communication) d'une application à une autre, la démarche « AAA » a été alors accompagnée par le souci d'exploiter cette caractéristique ou plus généralement de réduire les temps de conception et d'implantation de ces développements. Ainsi aux cours des travaux de recherche décrits dans la suite de ce paragraphe, nous avons proposé:

- ✓ la réutilisation de plateformes logicielles/matérielles (SW/HW) et de bibliothèques spécifiques pour diminuer le temps nécessaires à la validation des accélérateurs,

- √ l'évaluation de l'utilisation de la modélisation haut niveau et des outils associés de synthèse de haut niveau (HLS) pour le développement d'accélérateurs logiciels et ou matériels.

# 3.2 Plateforme de co-traitement destinée à la validation d'accélérateurs matériels

Le projet consistait en la conception d'une plateforme « Recherche et Développement », plateforme unifiée de co-processing pour implantation Software/Hardware de traitements vidéo. Ce projet a été initié au sein du comité MPEG, auquel j'ai participé activement jusqu'en 2009, pour un besoin de validation d'accélérateurs matériels sophistiqués et dédiés à la compression, et dont nous avons pu montrer par ailleurs qu'il était transposable plus généralement aux accélérateurs matériels dédiés au traitement d'images.

De nos jours, la compression et la décompression d'images numériques sont devenus des outils technologiques matures qui commencent à apparaître dans les applications de tous les jours tels que la télévision numérique, le stockage d'images numériques statiques, les web-cams. Cependant, la vidéo numérique est loin d'être utilisée à son potentiel maximum sur terminaux mobiles ou encore sur plate-formes PC standard. La raison principale réside dans le fait que les tâches de compression et de décompression nécessitent l'utilisation de plate-formes spécifiques dans le but de parvenir à une performance temps-réel. En général, les terminaux sont équipés de composants hardware spécifiques dans le but de réaliser les tâches de compression/décompression. C'est le cas de la télévision numérique et des webcams où des composants MPEG-2 sont en charge de l'intégralité du

chargement vidéo. Dans d'autres cas, la résolution vidéo est réduite dans le but de correspondre aux capacités de traitement des terminaux, même en utilisant des taux de transmission vidéo bien en dessous des capacités offertes par la bande passante du réseau ou des capacités de stockage. C'est le cas des terminaux mobiles de troisième génération (UMTS) or d'un PC portable sans capacités hardware qui lisent des fichiers vidéo au format DVX.

La difficulté d'intégrer les capacités nécessaires en termes de traitement dans les terminaux multimédia est accrue par le fait qu'un terminal ne doit pas seulement répondre à un simple algorithme spécifique de compression/décompression vidéo (vidéo standard) mais aussi à différents standards dépendant du type de matériel dont le terminal dispose ou de la connexion réseau imposée par le codeur spécifique. Si d'un côté les standards vidéo correspondent à des algorithmes très différents (H.261, MPEG-1, MPEG-2, H.263, MPEG-4 vidéo, MPEG/ITUT advanced video coding AVC, Movie JPEG2000, etc etc ...) car ils représentent l'état de l'art du codage vidéo au moment de leur définition, pour une gamme de taux de transmission spécifiques ou pour un ensemble spécifique de fonctionnalités (efficacité du codage, modularité, erreur ..., code orienté objet, etc, ...), d'un autre côté, ces standards partagent différents outils de codage utilisés dans des contextes différents ou avec des paramètres différents.

Ainsi l'idée de ce projet était de définir une plate-forme ouverte destinée au co-processing vidéo qui devait supporte des implémentations mixtes hardware/software, flexibles et reconfigurables, de codeur vidéo. Cette plate-forme avait pour ambition de correspondre dans le domaine de compression vidéo à l'équivalent de la librairie OpenGL dans le domaine graphique sur ordinateur. En d'autres termes, il s'agissait d'un ensemble de traitements codés à haut niveau tels que les blocs DCT, DWT, compensation de mouvement, estimation du mouvement, VLC, VLD, codage de forme, codage arithmétique, etc., et qui, grâce à la définition de leur API, seront exécutables par les « fonctions » de co-processing de la plate-forme, et ceci d'une manière complètement transparente pour l'application multimédia y faisant appel. Les fonctions ont été codées en VHDL ou Verilog et compatible avec la « PC-card WildCard » (Figure 8) comportant un FPGA de type Xilinx Virtex2 XCV300E.

Figure 8: Une PC-card à base de FPGA - La Wildcard

L'intervention du Le2i s'est effectuée en partenariat avec ses autres collaborateurs universitaires (Universités de Taïwan, de Calgary, de Dublin et l'Ecole Polytechnique Fédérale de Lausanne) et industriel (Xilinx). Le laboratoire Le2i a eu en charge le développement de la fonction d'estimation du mouvement présente dans la plupart des standards de compression vidéo récents. Le Le2i a été supporté financièrement par le contrat d'étude « Hors Contrats de Plan Etat-Région » (Référence: 04516CPO10S184) et a permis un certain nombre de contributions MPEG sur la période 2004-2008. Ce projet a été achevé avec succès en 2008. D'une part, il a permis d'atteindre les objectifs annoncés pour faciliter la mise en œuvre de codec vidéo. D'autre part, il a permis d'initier un projet plus ambitieux nommé « Reconficurable Video Coding » (RVC). Ainsi le développement d'un formalisme de type flot de données nommé CAL-RVC et des outils de prototypages rapides associés a été proposé comme plateforme de développement des futurs standards MPEG. A partir d'une description de ce type, il est possible de générer une partition logicielle et/ou matérielle. Les langages de description des décodeurs vidéo, le langage flot de données CAL-RVC permettant de décrire notamment l'ensemble des composants décodeurs ont été respectivement normalisés sous les noms MPEG-B Decoder Description Language (ISO 23001-4) (normative languages for the specification of a decoder configuration) et MPEG-C MPEG Toolbox (ISO 23002-4) (normative language for the specification of the toolbox).

En outre, nous avons cherché à montrer que cette plateforme pouvait être utilisée en dehors du domaine de la compression d'images. Ainsi la plateforme Wildcard a été utilisée dans le cadre de la thèse de Fethi Smach. Cette thèse portant sur la reconnaissance de formes a été dirigée par le Professeur Johel Mitéran. Les applications de reconnaissance de formes représentent un nombre croissant d'application de la vision artificielle au domaine industriel. La littérature abonde de techniques en reconnaissance de formes. Bon nombre de ces études ont pour objectifs de résumer une image à un nombre réduit de descripteurs qui ont comme propriété d'être invariants notamment aux déplacements (translation, rotation). Considérant les déplacements dans le plan, Gauthier et al [6] ont proposé une famille d'invariants, appelés descripteurs de mouvement, qui sont invariants en translation, en rotation, insensible aux changements d'échelle et à l'effet miroir. H. Fonga [7] a étendu l'utilisation des descripteurs de mouvement, définis de manière identique à ceux de Gauthier mais appliqués aux images en niveau de gris. Notre but, ici, était de montrer que tels descripteurs pouvaient être utilisés de manière souple et robuste pour la reconnaissance de formes basées sur des images couleur. Les descripteurs sont utilisés pour alimenter un classifieur de type « Support Vector Machine » (SVM), qui est une méthode supervisée. Les SVM cherchent un hyperplan permettant de séparer l'ensemble d'apprentissage de sorte que tous les points d'une même classe soient d'un même côté de l'hyperplan. Parmi l'ensemble des hyperplans satisfaisant ces conditions, les SVM cherchent celui qui maximise la distance entre l'hyperplan et les points les plus proches de chaque classe. Nous appliquons les phases classiques d'apprentissage et de décision ( Figure 9) de la manière suivante :

- ✓ L'image est redimensionnée au format 128x128 pixels.

- ✓ La FFT2D est calculée pour les 3 canaux rouge, vert et bleu.

- ✓ Les descripteurs de Fourier généralisés sont calculés pour chaque canal.

✓ L'ensemble des descripteurs (soit 3x64=192 valeurs) est utilisé pour alimenter le classifieur, qui génère un modèle en ce qui concerne la phase d'apprentissage, ou classe l'élément inconnu en ce qui concerne la phase de décision.

Au cours de la phase de décision, les descripteurs sont calculés de manière identique à la phase d'apprentissage. La prise de décision s'effectue directement grâce à la fonction de décision des SVM.

Figure 9. Phase d'apprentissage et phase de décision